# Control of Sidewall Profile in Dry Plasma Etching of Polyimide

Michal Zawierta, Mariusz Martyniuk, *Member, IEEE*, Roger D. Jeffery, Gino Putrino, Adrian Keating, *Senior Member, IEEE*, K. K. M. B. Dilusha Silva, *Member, IEEE*, and Lorenzo Faraone, *Fellow, IEEE*

Abstract—Spin-on polyimide is an organic thin film often used as a sacrificial layer for surface micromachining due to its high thermal stability, ease of removal, and compatibility with many materials and processes used in the realization of microelectromechanical systems (MEMS). The incorporation of sloped sidewalls in polyimide for fabricating pedestal structures is crucial in order to provide strong anchors in freestanding MEMS devices, especially in cases having a high aspect ratio and/or where structural materials have limited deposition conformality. This paper demonstrates a reliable reactive ion etching (RIE) methodology for tuning the polyimide sidewall angle, ranging from a vertical sidewall up to an angle of about 25° from the vertical. The key modifications to the process parameter space include changes to the process temperature and chamber pressure. This paper also presents a novel lift-off process, which is based on the use of an interfacial polymer layer to facilitate removal of an overlying silicon oxide hard mask. This procedure allows polyimide sacrificial layers employing a silicon oxide hard mask to be used on samples that have exposed silicon oxide layers elsewhere on the chip that are required to remain intact during hard mask removal. Therefore, this lift-off process is applicable in situations where the silicon oxide hard mask removal cannot be accomplished by wet etching in hydrofluoric acid solutions. [2016-0314]

Index Terms—Polyimide, plasma etching, reactive-ion etching, sidewalls, lift-off, sacrificial layer.

#### I. INTRODUCTION

RGANIC sacrificial layers are commonly used to support structural layers during surface micromachining of microelectromechanical systems (MEMS). They provide controllable layer thickness using a simple spin-on process, can survive a wide variety of surface micromachining processes, and can easily be removed through a dryrelease method in order to avoid the stiction issues associated with wet release processes. Organic polymer sacrificial layers include standard lithography photoresists [1], [2], polyimides

Manuscript received December 22, 2016; revised February 24, 2017; accepted March 8, 2017. Date of publication March 28, 2017; date of current version May 31, 2017. This work was supported in part by the Australian Research Council and in part by Panorama Synergy Ltd. Subject Editor Y. Zohar.

M. Zawierta, M. Martyniuk, R. Jeffery, G. Putrino, K. K. M. B. D. Silva, and L. Faraone are with the School of Electrical, Electronic and Computer Engineering, University of Western Australia, Crawley, WA 6009, Australia (e-mail: michal.zawierta@research.uwa.edu.au).

A. Keating is with the School of Mechanical and Chemical Engineering, University of Western Australia, Crawley, WA 6009, Australia.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JMEMS.2017.2681106

(e.g., HD Microsystems PI-2610, PI-2611 or Brewer Science ProLIFT) [3], [4], epoxy-based photoresists (e.g., SU-8) [5], and water-soluble polymers [6]. Of these, HD Microsystems polyimides are of considerable importance for micromachining applications since, in addition to being able to be removed with a pure oxygen plasma, they can withstand processing temperatures of up to 400 °C.

Dry etching of polyimides has been extensively explored with the aim of controlling the sidewall angle of the anchors used to support suspended structural layers. Mimoun *et al.* [7] developed an etch recipe which combined isotropic and anisotropic plasma etching to obtain a wine glass shaped sidewall profile in polyimide vias using sequential etching in two separate chambers. In comparison, the recipes developed in this paper use only a single etch process in a single chamber to achieve tapered sidewalls.

Deschler and Balk [8] investigated the influence of O<sub>2</sub>/CF<sub>4</sub> gas composition on the sidewall profile of etched structures in 2  $\mu$ m thick polyimide layers using photoresist as a mask. Their approach was similar to that of Till et al. [9], who developed a recipe for RIE etching of polyimide (Hitachi PIQ) in a pure oxygen plasma to control the sidewall slope. Till et al. [9] achieved control of the sidewall profile through the use of a photoresist erodible mask on a 1.5  $\mu$ m thick polyimide layer by careful control of the etching conditions, although the presented process is limited by the thickness of the photoresist mask. However, for thick polyimide films (> 5  $\mu$ m) a thicker photoresist masking layer is required, and the process that provides high selectivity to the photoresist mask is characterised by a low polyimide etch rate (maximum about 180 nm/min). Pham et al. [10] presented an etch recipe based on pure oxygen plasma for relatively thin 1.0  $\mu$ m – 2.5  $\mu$ m thick HD Microsystems PI-2610 polyimide sacrificial layers. However, their process leads to the formation of unwanted residues, which is a major issue. They also investigated the use of O<sub>2</sub>/He gas mixtures to reduce the residue level, but those mixtures affected the anisotropy of the etching profiles. Chen et al. [11] developed several polyimide etch recipes to investigate the influence of O<sub>2</sub>/SF<sub>6</sub> gas ratio on the etch rate and sidewall profile. They investigated relatively high pressure RIE recipes (600 mTorr) in which the ratio of O<sub>2</sub> to SF<sub>6</sub> varied from 50% to 100%, and reported on the resultant unusual sidewall profiles. Lee et al. [12] investigated similar polyimide dry etch recipes for the fabrication of thin film transistors (TFT), based on an O<sub>2</sub>/SF<sub>6</sub> chemistry, but

1057-7157 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

with the addition of Ar gas. Etching was performed using capacitively coupled plasma reactive-ion etching (CCP-RIE) at a pressure of 100 mTorr and RF power of 100 W, whereas Chen *et al.* [11] used 300 W. In addition, Lee *et al.* [12] investigated the details of the plasma chemistry during the etching process using optical emission spectroscopy (OES).

The avoidance of any post-processing residues is an important issue during polyimide etching [13] which, in general, can be avoided by using gas mixtures other than pure oxygen. Various gas mixtures have been proposed to avoid the formation of contaminant residues. Turban and Repeaux [14] used O<sub>2</sub>/CF<sub>4</sub> and O<sub>2</sub>/SF<sub>6</sub> plasmas to etch polyimide for a desmearing process during printed circuit board production, and analyzed the influence of different gas mixtures on the etching process. Bliznetsov *et al.* [15] also considered different gas mixtures at various plasma power levels to achieve a vertical polyimide sidewall profile, based on a high-throughput polyimide etching process using O<sub>2</sub>/CF<sub>4</sub> chemistry in a dual frequency RIE tool. In addition, Ma *et al.* [16] investigated the influence of the bias plate power on the residues remaining after etching in pure O<sub>2</sub> plasma.

Dry etching of thick polyimide films with a standard photoresist mask is not feasible due to the lack of durability of the photoresist in a plasma environment, and thus other masking materials with higher etch selectivity to polyimide are required. Bagolini et al. [17] investigated O<sub>2</sub>/CF<sub>4</sub> dry etching of HD Microsystems PI-2610 polyimide  $(2 \mu m - 4 \mu m \text{ thick})$  using several different materials as a masking layer, including aluminium, silicon carbide, and silicon oxide. In their study, silicon oxide was selected as the preferred option due to its better adhesion to polyimide compared to aluminium, and because it is easier to remove than silicon carbide. Additionally, they investigated the chemical resistance of polyimide to the various solvents used for cleaning the wafers between processing steps. Arevalo et al. [18] presented a surface micromachining process that used a gold structural layer as a hard mask for dry polyimide etching. For application in which gold is suitable to serve as the structural layer, their approach simplifies the fabrication process by avoiding the need for a separate hard mask.

Zulfigar et al. [19] presented etching processes for 10  $\mu$ m to 30  $\mu$ m thick polyimide layers based on two different hard mask materials (SiN<sub>x</sub> and Al). Their investigation included the influence of plasma chemistry, RF and ICP power, and chamber pressure on the etch rate of polyimide. Their analysis covered plasmas with pure O<sub>2</sub>, O<sub>2</sub>/Ar, O<sub>2</sub>/CF<sub>4</sub> and O<sub>2</sub>/SF<sub>6</sub> mixtures. Vertyanov et al. [20] presented etching processes for 25  $\mu$ m and 76  $\mu$ m thick polyimide films, where they examined the influence of the gas composition (O2, Ar and SF6) and RF power on the process etch rate. However, it needs to be noted that the influence of chamber pressure on the etching of polyimide layers thicker than 5  $\mu$ m and at elevated process temperature (in our case, 100 °C) has not been previously documented in the open literature. Such thick sacrificial layers are often necessary in order to reduce squeezed film damping of the fabricated free-standing structures, which may be suspended several micrometres above the substrate surface [21]. For example, high structures with tapered sidewalls are essential for MEMS ionization gas sensors [22]. The features of the proposed polyimide etch recipe can also be used for fabrication of polyimide based variable focus microlenses [23] as well as for angled mirrors for planar silicon photonics [24], [25] where tapered sidewalls are essential.

This work describes a residue-free anisotropic plasma etching process for thick polyimide layers, with the added ability to precisely control the sidewall profile. The sidewall angle is a key parameter required for fabricating free-standing structures based on thin films deposited with limited conformality using thermal evaporation or most plasma-enhanced chemical vapor deposition (PECVD) techniques. Although the steep slope of the polyimide sidewall is likely to significantly limit the layer thickness deposited on the sidewalls, the controlled profile can be used to improve sidewall coverage to some extent.

In this paper, we have studied the influence of chamber pressure on the polyimide etching process at elevated processing temperatures, and have investigated the mechanism which determines the sidewall angle. In addition, this work introduces a hard mask lift-off process based on an interfacial polymer layer for removal of the overlying hard mask.

#### II. EXPERIMENTAL PROCEDURES

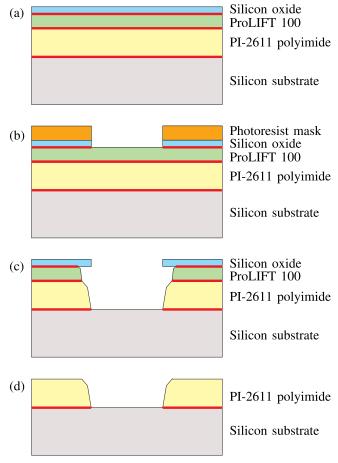

The polyimide etching experiments were performed using an inductively coupled plasma reactive etching (ICP-RIE) Plasmalab System 100 tool from Oxford Instruments. In this system a 4-inch diameter, 300 µm thick, <100> silicon carrier wafer is mechanically clamped to the heated sample table and back-side helium is introduced to provide good thermal contact between the table and carrier wafer. Before commencing the etching process, the sample table temperature was set and allowed to stabilize. The experiments were performed using polished square <100> silicon substrates (2×2 cm<sup>2</sup>) of 300  $\mu$ m in thickness. The experiments were also repeated on 2-inch diameter silicon <100> substrates with the same thickness as the  $2\times2$  cm<sup>2</sup> samples in order to assess the influence of loading effects on the etching process. A schematic of the adopted process flow is shown in Fig. 1. The bare silicon substrates were covered with Brewer Science APX-K1 adhesion promoter, which was selected in preference to the VM-651 recommended by HD MicroSystems (manufacturer of the PI-2611 polyimide) due to easier storage and usage specifications. The APX-K1 adhesion promoter is premixed and ready to use, whereas VM-651 needs to be diluted before each use. The adhesion promoter was found to be necessary between each layer in the procedure in order to avoid delamination of the polyimide from the substrate, as well as delamination between subsequently deposited layers.

The substrates were then spin-coated with a thick polyimide layer (HD MicroSystems PI-2611) in a two-step spinning cycle. Firstly, a rotation speed of 500 rpm for 5 seconds was used to spread the dispensed material on the surface, followed by 2000 rpm for 40 seconds to achieve the desired thickness, typically in the range of 8  $\mu$ m – 9  $\mu$ m thick. After spin-coating with PI-2611, the samples were soft baked in ambient

Fig. 1. Polyimide sacrificial layer fabrication process: (a) spin, bake and cure of HD Microsystems PI-2611 polyimide layer, followed by spin-coating of Brewer Science ProLIFT 100, followed by deposition of  $\mathrm{SiO}_{\mathrm{X}}$  hard mask; (b)  $\mathrm{SiO}_{\mathrm{X}}$  patterning using reactive-ion etching and a standard photoresist mask; (c) polyimide etch process using one of the specific recipes developed in this paper; (d) hard mask removal via lift-off in positive photoresist developer, leaving the polyimide sacrificial layer with tapered sidewalls for subsequent processing. The thick (red) interlayer lines represent layers of APX-K1 adhesion promoter.

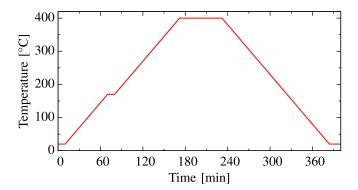

laboratory conditions on a hotplate for 90 seconds at 90 °C, followed by another 90 seconds at 150 °C. Subsequent curing of the polyimide was completed in a nitrogen atmosphere on a hot plate using the heating/cooling profile shown in Fig. 2, and completely cured at a temperature of 400 °C for one hour. The initial soft bake at 90 °C and 150 °C allows stacking of multiple layers of polyimide in order to achieve very thick sacrificial layers [26], whereas the later high-temperature curing process given by the temperature profile in Fig. 2 produces a stable film with the desired parameters.

A layer of Brewer Science APX-K1 adhesion promoter was applied on top of the PI-2611 polyimide layer to obtain adequate adhesion of the overlying Brewer Science Pro-LIFT 100 layer, and thus avoid the risk of delamination at the interface, as schematically indicated in Fig. 1 by the thick red interfaces. The etching mask consisted of the ProLIFT 100 polyimide layer (about 3.5  $\mu$ m thick) and an overlying silicon oxide thin film layer (about 1  $\mu$ m thick). The ProLIFT 100 was spin-coated on the surface of the PI-2611 polyimide, soft baked at 135 °C for 90 seconds and then cured at 300 °C for 30 minutes. Next, a layer of

Fig. 2. Temperature profile for curing polyimide in a nitrogen atmosphere. A ramp rate of 3  $^{\circ}$ C/min was used for the heating and cooling steps. The hold times consist of 5 minutes at 170  $^{\circ}$ C for solvent evaporation, and 1 hour at 400  $^{\circ}$ C for complete polyimide curing.

APX-K1 adhesion promoter was deposited just before silicon oxide deposition in an inductively coupled plasma chemical vapor deposition (ICP-CVD) system at a substrate temperature of 275 °C (see Fig. 1). Brewer Science ProLIFT 100 [4] are polyimides that are soluble in positive resist (alkaline) developers after imidization by baking, but retain high resistance to acid etchants, organic solvents, and high process temperatures. PI-2611 is a non-photodefineable, dry etch polyimide, which in contrast to ProLIFT 100, is not soluble in positive resist developers after full curing. The solubility of ProLIFT 100 in positive resist developers allows lift-off of the silicon oxide hard mask in a wet process after dry etching of PI-2611 polyimide has been completed, without affecting the PI-2611 sacrificial layer.

The silicon oxide hard mask was patterned using a photoresist mask and etched in CF<sub>4</sub> using an Oxford Plasmalab System 100 ICP-RIE system. The developed process flow does not require a separate step to remove the photoresist used to pattern the silicon oxide hard mask before commencing the polyimide etching process, since the polyimide etch process will also rapidly remove the photoresist and leave a residue-free top surface. The etch rate of the SiO<sub>x</sub> hard mask was determined to be between 15 nm/min and 20 nm/min, and the thickness was set to 1  $\mu$ m in order to ensure good edge definition in subsequent imaging processes. For routine processing, the thickness of the hard mask can be reduced, for example, to 400 nm of SiO<sub>x</sub> for a 9  $\mu$ m thick polyimide film. A summary of all processing steps, preceding polyimide etching, are listed in Table I.

The adopted polyimide etching chemistry was based on the work of Mimoun  $et\ al.\ [7]$ , which consisted of  $80\%\ O_2$ ,  $13\%\ N_2$ , and  $7\%\ CF_4$ . In the present paper, the desired etch characteristics were achieved by setting the substrate stage temperature to  $100\ ^{\circ}\text{C}$ , and varying the chamber pressure between 5 mTorr and 40 mTorr to tune the sidewall profile. The temperature of  $100\ ^{\circ}\text{C}$  was chosen experimentally as a minimum value to achieve stable and repeatable etching results. Prior to commencing the etching process, the samples were placed on top of the carrier wafer. Additional thermally conductive material was not introduced between the samples and the carrier wafer, since trial runs indicated adequate

TABLE I

DETAILED FABRICATION PROCEDURE FOR POLYIMIDE SAMPLES PRIOR TO POLYIMIDE ETCHING

Clean silicon substrate wafer

Spin adhesion promoter Brewer Science APX-K1 (4000 rpm/40 s)

Bake APX-K1 on the hotplate (175 °C/40 s)

Spin HD Microsystems PI-2611 (500 rpm/5 s followed by 2000 rpm/40 s)

Soft-bake PI-2611 on the hotplate (90 °C/90 s, followed by 150 °C/90 s)

Cure PI-2611 on the hotplate (400 °C/1 hour, heating/cooling ramp rate 3 °C/min: see Fig. 2)

Spin adhesion promoter Brewer Science APX-K1 (4000 rpm/40 s)

Bake APX-K1 on the hotplate (175 °C/40 s)

Spin Brewer Science ProLIFT 100-24 (500 rpm/5 s, next 4000 rpm/90 s)

Soft-bake ProLIFT 100-24 on the hotplate (135 °C/90 s)

Cure ProLIFT 100-24 on the hotplate (300 °C/30 min)

Spin adhesion promoter Brewer Science APX-K1 (4000 rpm/40 s)

Bake APX-K1 on the hotplate (175 °C/40 s)

Deposit SiO<sub>x</sub> hard mask using ICP-CVD deposition tool (275 °C/1 hour)

gas flow:  $SiH_4 = 6.5$  sccm, He = 123 sccm, Ar = 126 sccm,  $N_2O = 70$  sccm; pressure: 2 Pa; ICP power: 450 W.

Sample at this stage corresponds to that shown in Fig. 1(a)

Pattern SiO<sub>x</sub> hard mask using ICP-RIE etching tool with photoresist mask (20 °C/26 min)

gas flow: CF<sub>4</sub> = 34 sccm; pressure: 10 Pa; RF power: 100 W; ICP power: 400 W.

Sample at this stage corresponds to that shown in Fig. 1(b)

TABLE II

POLYIMIDE PLASMA ETCH RECIPE DETAILS

| Parameter            | Value        |

|----------------------|--------------|

| O <sub>2</sub> flow  | 60.0 sccm    |

| $N_2$ flow           | 9.8 sccm     |

| CF <sub>4</sub> flow | 5.2 sccm     |

| ICP Power            | 200 W        |

| RF Power             | 100 W        |

| Stage temperature    | 100 °C       |

| Pressure             | 5 – 40 mTorr |

| He backing pressure  | 10 Torr      |

process stability and performance. The carrier wafer was loaded into the etching chamber and mechanically clamped to the heated table. Helium gas was introduced between the carrier wafer and the heated table to achieve good thermal contact and allow efficient heating of the carrier wafer. The samples remained in that condition for 15 minutes for temperature equilibration before processing commenced. During the etching process the temperature on the surface of the sample may increase due to plasma heating, which can be an advantageous characteristic since the localized increase in temperature may locally speed up the etching reactions. This phenomenon could be explored further to achieve local sidewall tapering just under the hard mask, if desired. The ICP and RF power were chosen experimentally in order to achieve a stable and repeatable etch profile with relatively high etch rates. The chamber pressure during the etching process has a significant influence on the resulting polyimide pedestal slope [27]. Mimoun et al. [7] did not provide any additional details on their recipe or the equipment they used. The details of the plasma etch recipes developed in the present study are summarized in Table II.

After the polyimide etching experiments, the samples were placed in an AZ326 photoresist developer bath (an aqueous solution of 2.38% tetramethyl ammonium hydroxide (TMAH)) in order to dissolve the ProLIFT 100 layer and lift-off the silicon oxide hard mask. This process required up to a few hours to complete when polyimide etching was performed through small openings in the hard mask. However, it is noted that the process consistently resulted in a residue-free and undamaged surface of the PI-2611 polyimide, and guaranteed removal of the hard mask.

# III. RESULTS AND DISCUSSION

To evaluate the etching process, two series of experiments were performed, each having multiple samples that were prepared and etched in a separate fabrication process, and the cross-section of each sidewall profile was obtained using a focused-ion beam (FIB) and a scanning electron microscope (SEM). During the first series of experiments, the samples were etched with a common recipe but with the etching time being varied between 1 and 20 minutes. This allowed the progress of the etching of the polyimide sacrificial layer to be evaluated. During the second series of experiments, each sample was etched until all the polyimide was removed under different chamber pressure in the range between 5 and 40 mTorr for individual samples.

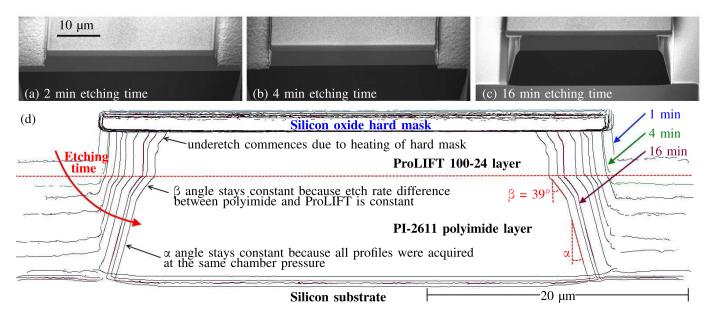

### A. Etch Profile Time Evolution

The first series of experiments consisted of ten samples, each etched for a different etching time, with the first sample being etched for 1 minute. The etching time for the remainder of the samples was progressively increased from 4 to 20 minutes in steps of 2 minutes. Fig. 3(a)–(c) show SEM images of the cross-sectional etch profiles for three selected samples. The profiles of the etched structures shown

Fig. 3. Cross-sections of the etched sample structures for different etching times. Ten separate samples were etched using the same recipe (see Table II, with pressure = 10 mTorr) for different etch times, starting with 1 minute and then from 4 minutes up to 20 minutes in 2-minute increments. The measured profiles were aligned to the bottom surface of the  $SiO_x$  hard mask. The indicated scale is common to (a)–(c) images.

in Fig. 3(d) were extracted from the SEM images by an edge detection filter using ImageJ 1.50i software in order to allow for a precise comparison between the samples. The obtained profiles were stacked together on one image to show the time-evolution of the etching profile (see Fig. 3(d)).

As evident from Fig. 3(d), two distinct slopes ( $\alpha$  and  $\beta$ ) can be distinguished on the sidewall of the PI-2611 polyimide layer. The ICP-RIE etching process consists of two components: physical and chemical etching. The physical etching component is associated with close to vertical ion bombardment of the exposed part of the polyimide and is mainly responsible for obtaining straight vertical sidewalls. The chemical etching component is associated with the reactive species of the plasma chemically etching the polyimide material equally in all directions, and is primarily responsible for the horizontal etching of polyimide since the sidewalls are partially protected from ion bombardment by hard mask shadowing. Both physical and chemical etching components are associated with vertical etch of polyimide. As the polyimide is etched vertically, an increasing amount of sidewall depth is exposed which then allows horizontal chemical etching to occur. Since both the horizontal and vertical etching occur simultaneously, the horizontal etching of the sidewall creates sloped sidewalls as the upper parts of the polyimide sidewall are progressively exposed and etched for longer than the lower sidewall parts (angle  $\alpha$  for PI-2611 polyimide). The same reasoning can be used to explain the angle of the main sidewall slope of the overlaying ProLIFT layer (lower portion of the ProLIFT sidewall). Note that the ion bombardment enhanced vertical component of the etching process dominates the horizontal component more prominently for ProLIFT than for PI-2611, which results in a steeper sidewall profile for the ProLIFT layer. The upper sidewall slope of the PI-2611 polyimide layer (angle  $\beta$  in Fig. 3(d)),

is a consequence of the difference in the etch rates between the ProLIFT and the underlying PI-2611 polyimide. Since the horizontal etch rate of the ProLIFT is significantly higher than the PI-2611 polyimide layer, progressively more PI-2611 top surface is exposed for chemical etching. This allows chemical etching of the exposed upper surface of the PI-2611 to progress at the same time as etching in the horizontal direction, which results in the formation of a slope angle  $\beta$ .

The slight undercut which is present just below the hard mask in the ProLIFT 100 is likely due to localized heating of the SiO<sub>x</sub> hard mask caused by ion bombardment during the long etching process. Although the ion energy does not cause significant etching of the hard mask, it can increase the temperature of the masking layer. Since this heat is not dissipated efficiently to the substrate due to low thermal conductivity of the thick underlying polymer layers, there is likely to be a significant increase in the local SiO<sub>x</sub> temperature [28], [29]. Thus, in comparison to the bulk of the ProLIFT, the increased temperature just under the SiO<sub>x</sub> hard mask will result in faster chemical etching of the ProLIFT surface [30], [31], resulting in an increased lateral etch rate directly under the mask. The faster etch rate directly under the mask is observed on the cross-sectional profiles presented in Fig. 3(d) to commence after a few minutes of etching once the temperature of the hard mask has increased sufficiently.

### B. Etch Profile Slope Control

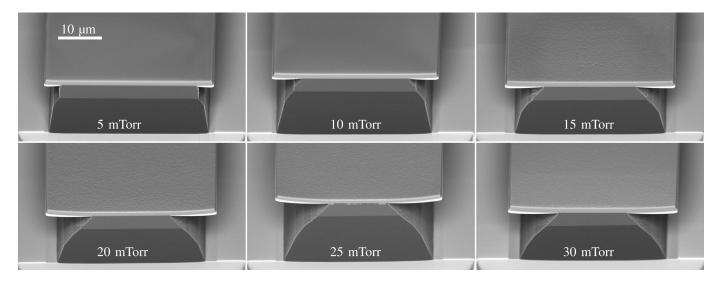

The second series of experiments investigated the influence of the chamber gas pressure on the sidewall profile of the etched polyimide layers, with the chamber pressure being varied between 5 and 40 mTorr. The SEM images showing the cross-sections of the etched structures are presented in Fig. 4, which indicate that pressure has a significant influence on

Fig. 4. SEM images of cross-sections of etched patterns of ProLIFT/PI-2611 polyimide stacks with  $SiO_X$  hard mask on top for various etching chamber pressures. Note that there are no organic residues on the silicon substrate after polyimide etching. The white layer visible on the images on the underside of the  $SiO_X$  hard mask as well as on the substrate, is gallium residue deposited during FIB milling used to prepare the cross-sections of the etched profiles. The indicated scale is common to all images.

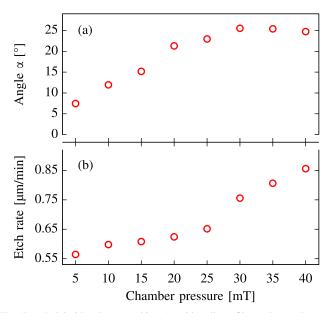

Fig. 5. Polyimide plasma etching (a) sidewall profile angle (angle  $\alpha$  as defined in Fig. 3(d) for the main lower portion) and (b) etch rate as a function of chamber pressure for an etching temperature of 100 °C.

the sidewall profile. The  $\alpha$  angle for the lower part of the PI-2611 polyimide slope varies significantly as a function of chamber pressure, and this relationship is shown in Fig. 5(a). Our observations indicate that an overall increase in the etch rate of PI-2611 is associated with increasing process pressure, and that the  $\hat{\mathbf{l}}\pm$  angle of the PI-2611 polyimide can be modified by chamber pressure control.

The  $\alpha$  angle of the PI-2611 sidewall profile was found to vary from 8° from the vertical for 5 mTorr pressure to about 25° for pressures of 30 mTorr and above. In contrast, the angle of the upper portion of the PI-2611 sidewall was found to be independent of the chamber pressure, and found to be close to 40° from the vertical.

In addition, and as presented on Fig. 5(b), within the range of the investigated process pressures, we observed a strong positive correlation between the etch rate and chamber pressure. The lowest etch rate of PI-2611 polyimide (570 nm/min) was achieved for the lowest process pressure (5 mTorr), and the highest etch rate of PI-2611 polyimide (860 nm/min) was achieved for the highest process pressure (40 mTorr).

To verify the influence of loading effects on the etch rate, we repeated selected experiments on 2-inch diameter silicon wafers. The etch rates and sidewall profiles of the polyimide measured on 2-inch wafers were found not to be noticeably different in comparison to the smaller samples examined in this paper  $(2 \times 2 \text{ cm}^2)$ . While isotropic etching of larger samples may give rise to edge effects, our observations agree with the findings of Turban and Repeaux [14], where no noticeable loading effects were observed in the low-pressure regime.

The overall positive correlation between the  $\hat{I}\pm$  angle and process pressure can be attributed to increasing chamber pressure enhancing the chemical etch rate component, whereas the ion bombardment enhanced vertical component of the etch rate remains unaffected or increases at a lower rate than the chemical etch rate [32]. These differences appear to be the principal reasons for sidewall profile variability with chamber pressure.

### C. Hard Mask

An additional outcome reported in this paper is the hard mask lift-off process used to remove the  $\mathrm{SiO}_x$  hard mask subsequent to the etching of the polyimide. This process allows patterning of the polyimide sacrificial layer and removal of the silicon oxide hard mask in a positive photoresist developer, i.e. a weak base solution. We avoided the use of hydrofluoric acid solutions to remove the oxide mask due to the fact that any exposed oxide layers that may be required to remain elsewhere on the chip would also have been etched.

During our process development, the SiO<sub>x</sub> hard mask was liable to delaminate causing under-etch around the mask pattern. This phenomenon was similar to that previously reported with the usage of metal hard masks [17]. Such delamination is often attributed to residual stress in the deposited masking thin film, as well as to any differences in thermal expansion coefficients between the layers, which can lead to cracks and delamination near the etch holes [33]. All of these issues were eliminated using the adhesion promoter APX-K1, which was applied between all interlayers. Application of an adhesion promoter is recommended by the PI-2611 polyimide manufacturer [3].

#### IV. CONCLUSIONS

We have demonstrated a novel approach for the fabrication of polyimide sacrificial layers through polyimide etching at elevated temperatures. The developed recipes allow residue-free etching with a controlled sidewall profile, and result in high-quality surfaces. The sacrificial layer sidewall angle can be controlled by varying the chamber pressure during the etching process. The etching was conducted with a double layer mask consisting of a SiO<sub>x</sub> hard mask and a ProLIFT underlayer that was subsequently used to lift-off the SiO<sub>x</sub> thin film hard mask after etching of the PI-2611 polyimide layer. As such, the mask removal process was carried out in non-agressive positive photoresist developer, which allows fabrication of sacrificial layers with high-quality surfaces that are not attacked during hard mask removal.

We have achieved etch rates up to  $0.86~\mu$ m/min, while the sidewall angle from the vertical can be controlled from between  $8^{\circ}$  to about  $25^{\circ}$ . A single etch of  $9~\mu$ m thick polyimide layer takes between 10 to 16 minutes, depending on the pressure of the process; however, higher etch rates may be possible by increasing the RF and/or ICP power.

#### ACKNOWLEDGMENTS

This work was performed at the Western Australian node of the Australian National Fabrication Facility, a company established under the National Collaborative Research Infrastructure Strategy to provide nano and microfabrication facilities for Australia's researchers. The authors acknowledge the facilities, and the scientific and technical assistance of the Australian Microscopy & Microanalysis Research Facility at the Centre for Microscopy, Characterisation & Analysis, The University of Western Australia. The above facilities have been funded by the University, State and Commonwealth Governments.

# REFERENCES

- [1] K. Walsh, J. Norville, and Y.-C. Tai, "Photoresist as a sacrificial layer by dissolution in acetone," in *Proc. 14th IEEE Int. Conf. Micro Electro Mech. Syst. (MEMS)*, Jan. 2001, pp. 114–117.

- [2] D. Molinero and L. Castaner, "MEMS switches fabrication using photoresist as a sacrificial layer," in *Proc. Spanish Conf. Electron Dev. (CDE)*, Feb. 2009, pp. 281–284.

- [3] HD MicroSystems. (Sep. 2009). PI-2600 Series—Low Stress Applications. [Online]. Available: http://www.dupont.com/content/dam/dupont/ products-and-services/electronic-and-electrical-materials/semiconductor -fabrication-and-packaging-materials/documents/PI-2600\_Process Guide.pdf

- [4] ProLIFT 100 Lift-Off Release, Brewer Science, Inc., Rolla, MO, USA, Sep. 2010.

- [5] C. Chung and M. Allen, "Uncrosslinked SU-8 as a sacrificial material," J. Micromech. Microeng., vol. 15, no. 1, pp. N1–N5, Jan. 2005.

- [6] V. Linder, B. D. Gates, D. Ryan, B. A. Parviz, and G. M. Whitesides, "Water-soluble sacrificial layers for surface micromachining," *Small*, vol. 1, no. 7, pp. 730–736, Jul. 2005.

- [7] B. Mimoun, H. T. M. Pham, V. Henneken, and R. Dekker, "Residue-free plasma etching of polyimide coatings for small pitch vias with improved step coverage," *J. Vac. Sci. Technol. B, Microelectron. Process. Phenom.*, vol. 31, no. 2, p. 021201, Mar. 2013.

- [8] M. Deschler and P. Balk, "Optimization of via hole plasma etching in polyimide for overlay interconnections," *Microelectron. Eng.*, vol. 4, no. 3, pp. 207–219, 1986.

- [9] S. J. Till, A. G. Brown, and V. G. I. Deshmukh, "Reactive ion etching of polyimide for multi-level resist and contact hole applications," *Microelectron. Eng.*, vol. 3, nos. 1–4, pp. 491–498, Dec. 1985.

- [10] H. Pham et al., "Polyimide sacrificial layer for an all-dry post-process surface micromachining module," in Proc. 12th Int. Conf. Solid-State Sens., Actuators, Microsyst. (TRANSDUCERS), vol. 1. Jun. 2003, pp. 813–816.

- [11] Y. Chen et al., "Fabrication of polyimide sacrificial layers with inclined sidewalls based on reactive ion etching," AIP Adv., vol. 4, no. 3, p. 031328. Mar. 2014.

- [12] Y. J. Lee et al., "A study of dry etching characteristics of polyimide films in flexible displays with trench structures," Sci. Adv. Mater., vol. 8, no. 4, pp. 851–853, Apr. 2016.

- [13] Y. L. Tsang, C. Miller, and T. Lii, "Investigation of polyimide residue due to reactive ion etching in O<sub>2</sub>," *J. Electrochem. Soc.*, vol. 143, no. 4, pp. 1464–1469, Apr. 1996.

- [14] G. Turban and M. Rapeaux, "Dry etching of polyimide in O<sub>2</sub>-CF<sub>4</sub> and O<sub>2</sub>-CF<sub>6</sub> plasmas," *J. Electrochem. Soc.*, vol. 130, no. 11, pp. 2231–2236, Nov. 1983.

- [15] V. Bliznetsov, A. Manickam, J. Chen, and N. Ranganathan, "High-throughput anisotropic plasma etching of polyimide for MEMS," J. Micromech. Microeng., vol. 21, no. 6, p. 067003, Jun. 2011.

- [16] S. Ma, Y. Li, X. Sun, X. Yu, and Y. Jin, "Study of polyimide as sacrificial layer with O<sub>2</sub> plasma releasing for its application in MEMS capacitive FPA fabrication," in *Proc. Int. Conf. Electron. Packag. Technol. High Density Packag. (ICEPT-HDP)*, Aug. 2009, pp. 526–529.

- [17] A. Bagolini, L. Pakula, T. L. M. Scholtes, H. T. M. Pham, P. J. French, and P. M. Sarro, "Polyimide sacrificial layer and novel materials for post-processing surface micromachining," *J. Microelectromech. Syst.*, vol. 12, no. 4, p. 385. Jul. 2002.

- [18] A. Arevalo, E. Byas, D. Conchouso, D. Castro, S. Ilyas, and I. G. Foulds, "A versatile multi-user polyimide surface micromachinning process for MEMS applications," in *Proc. 10th IEEE Int. Conf. Nano/Micro Eng. Mol. Syst.*, Apr. 2015, pp. 561–565.

- [19] A. Zulfiqar, A. Pfreundt, W. E. Svendsen, and M. Dimaki, "Fabrication of polyimide based microfluidic channels for biosensor devices," J. Micromech. Microeng., vol. 25, no. 3, p. 035022, 2015.

- [20] D. Vertyanov, E. Byas, D. Conchouso, D. Castro, S. Ilyas, and I. G. Foulds, "Deep plasma etching process investigation of polyimide materials for forming interlayer connections in microelectronic nodes," in *Proc. IEEE 34th Int. Sci. Conf. Electron. Nanotechnol. (ELNANO)*, Apr. 2014, pp. 54–57.

- [21] T. Corman, P. Enoksson, and G. Stemme, "Gas damping of electrostatically excited resonators," *Sens. Actuators A, Phys.*, vol. 61, no. 1, pp. 249–255, Jun. 1997.

- [22] T. Walewyns, G. Scheen, E. Tooten, L. El Fissi, P. Dupuis, and L. A. Francis, "Fabrication of a miniaturized ionization gas sensor with polyimide spacer," *Proc. SPIE*, vol. 8066, p. 80660J, May 2011.

- [23] Y.-J. Chang, K. Mohseni, and V. M. Bright, "Fabrication of tapered SU-8 structure and effect of sidewall angle for a variable focus microlens using EWOD," Sens. Actuators A, Phys., vol. 136, no. 2, pp. 546–553, May 2007.

- [24] T. Nagata, T. Tanaka, K. Miyake, H. Kurotaki, S. Yokoyama, and M. Koyanagi, "Micron-size optical waveguide for optoelectronic integrated circuit," *Jpn. J. Appl. Phys.*, vol. 33, no. 1S, p. 822, Jan. 1994.

- [25] T. Nagata et al., "Single-chip integration of light-emitting diode, waveguide and micromirrors," Jpn. J. Appl. Phys., vol. 34, no. 2B, p. 1282. Feb. 1995.

- [26] P. Rai-Choudhury, Handbook of Microlithography, Micromachining, and Microfabrication: Micromachining and Microfabrication. Stevenage, U.K.: IET, Jan. 1997.

- [27] J. K. Bhardwaj and H. Ashraf, "Advanced silicon etching using high-density plasmas," *Proc. SPIE*, vol. 2639, pp. 224–233, Sep. 1995.

- [28] R. J. Visser, "Determination of the power and current densities in argon and oxygen plasmas by in situ temperature measurements," J. Vac. Sci. Technol. A, Vac. Surf. Films, vol. 7, no. 2, pp. 189–194, Mar. 1989.

- [29] B. C. Dems and F. Rodriguez, "The role of heat transfer during reactiveion etching of polymer films," J. Vac. Sci. Technol. B, Nanotechnol. Microelectron., Mater., Process., Meas., Phenomena, vol. 8, no. 6, pp. 1985–1989, Aug. 1990.

- [30] M. Ghosh, Polyimides: Fundamentals and Applications. Boca Raton, FL, USA: CRC Press, Jul. 1996.

- [31] J. Y. Jeong *et al.*, "Etching polyimide with a nonequilibrium atmospheric-pressure plasma jet," *J. Vac. Sci. Technol. A, Vac. Surf. Films*, vol. 17, no. 5, pp. 2581–2585, Sep. 1999.

- [32] F. F. Chen and M. D. Smith, "Plasma," in Van Nostrand's Scientific Encyclopedia. Hoboken, NJ, USA: Wiley, 2005.

- [33] T. Kitamura, H. Hirakata, and T. Itsuji, "Effect of residual stress on delamination from interface edge between nano-films," *Eng. Fract. Mech.*, vol. 70, no. 15, pp. 2089–2101, Oct. 2003.

Michal Zawierta was born in Poland, in 1986. He received the B.Sc. and M.Sc. degrees in electronics and telecommunication from the Wroclaw University of Technology, Wroclaw, Poland, in 2011 and 2012, respectively, and the B.Sc. degree in management from the Wroclaw University of Economics, Wroclaw, in 2011. He is currently pursuing the Ph.D. degree with the School of Electrical, Electronic, and Computer Engineering, University of Western Australia, Perth, WA, Australia. His current research activities involve optical

microelectromechanical systems.

Mariusz Martyniuk (M'12) was born in Poland. He received the B.Sc. degree (Hons.) from the University of Toronto, ON, Canada; the M.A.Sc. degree from McMaster University, ON, Canada; and the Ph.D. degree from the University of Western Australia, Perth, Australia, in 2007. He was with the industry sector as an Electronics Engineer. He is currently a Research Professor with the School of Electrical, Electronic, and Computer Engineering, University of Western Australia, and also manages the Western Australian Node of the Australian

National Fabrication Facility. His primary areas of interest encompass thin-film materials and thin-film mechanics, and their applications in micro-electromechanical systems and optoelectronic devices.

Dr. Martyniuk's research contributions were recognized by the award of the Inaugural Australian Museum Eureka Prize (the Oscars of Australian science) for Outstanding Science in Support of Defense or National Security in 2008.

Roger D. Jeffery received the B.Sc. degree in mathematics and computer science, and the B.E. degree from Adelaide University, Adelaide, SA, Australia, in 1972 and 1973, respectively, and the M.Eng.Sc. and Ph.D. degrees from the University of Western Australia (UWA), Crawley, WA, Australia, in 1979 and 1984, respectively.

He joined the Department of Electrical and Electronic Engineering, UWA, in 1973. From 1985 to 1986, he was an ARGC Research Fellow and a member of the original Networking Group with the

Department of Electrical and Electronic Engineering, UWA, where he was involved in QPSX technology, which was subsequently standardized as IEEE 802.6. He was involved in the communications industry and subsequently led several ASIC design teams from 1987 to 2004. He was involved in drivers for magnetooptic material. In 2005, he was a Contractor with ST Synergy Ltd., Perth, WA, Australia, (later becoming Panorama Synergy Ltd.). He was involved in magneto optics until 2015 and held several patent applications in this area. Since 2013, he has been involved in MEMs sensors using an optical readout. He is currently an Adjunct Associate Professor with the School of Electrical, Electronic, and Computer Engineering, UWA.

Gino Putrino was born in Perth, Australia, in 1976. He received the B.Sc. degree in computer science, and the B.E. degree in electrical and electronic engineering from the University of Western Australia, Perth, in 1999, and the Ph.D. degree in 2014. His current research activities involve the use of optical microelectro-mechanical systems and silicon photonics to create novel chemical and biological sensing devices.

Adrian Keating (M'90–SM'07) was born in Melbourne, Australia, in 1967. He received the B.E. degree (Hons.) and the Ph.D. (in photonics) degree in electrical and electronic engineering from the University of Melbourne, Australia, in 1990 and 1995, respectively. Since 1996, he has been with NTT Research Labs, Musashino, Japan; the University of California at Santa Barbara, Santa Barbara; and Calient Networks as the Fiber Optics Technology Manager. He joined the School of Electrical, Electronic, and Computer Engineering, University

of Western Australia, in 2004, and was then with the School of Mechanical Engineering, where he is currently an Associate Professor. His current research activities are in infrared optics sensors, sensor systems, optical microelectromechanical systems, and porous silicon-based sensor technologies.

K. K. M. B. Dilusha Silva (M'08) was born in Sri Lanka, in 1973. He received the degree (Hons.) in physics and electronics engineering, and the Ph.D. degree from the University of Western Australia (UWA), Perth, WA, Australia. He was with the industry and academia, and is currently a Research Professor and Engineering Manager with the Microelectronics Research Group, UWA. His research interests include optical microelectromechanical systems (MEMS) sensors, optical spectroscopic sensors, and MEMS biosensors. He has

attracted research funding from government and the agriculture and aerospace sectors, and he leads a number of MEMS research efforts with strong commercial links to both agriculture and aerospace.

Lorenzo Faraone (M'78–F'15) received the Ph.D. degree from the University of Western Australia (UWA) in 1979. He was a Research Scientist at Lehigh University, USA, from 1979 to 1980. He joined UWA in 1987. He has supervised over 35 Ph.D. student completions and authored over 250 refereed journal papers. His research interests have been in the area of infrared semiconductor materials and devices and microelectromechanical systems. From 1980 to 1986, he was a member of Technical Staff at RCA Laboratories, Princeton, NJ,

USA, where he was involved in CMOS nonvolatile memory technologies and space radiation effects in silicon-on-sapphire MOS integrated circuits. He is a member of the Order of Australia, and a fellow of the Australian Academy of Science and the Australian Academy of Technology and Engineering.