# A High Deposition Rate Amorphous-Silicon Process for Use as a Thick Sacrificial Layer in Surface-Micromachining

Michal Zawierta, Mariusz Martyniuk, *Member, IEEE*, Roger D. Jeffery, Gino Putrino, Adrian Keating, *Senior Member, IEEE*, K. K. M. B. Dilusha Silva, *Member, IEEE*, and Lorenzo Faraone, *Fellow, IEEE*

Abstract-Amorphous and polycrystalline silicon are commonly used as sacrificial layers in the surface micromachining of microelectromechanical systems (MEMS) devices, because they have high thickness uniformity over a large wafer area, and a similar coefficient of thermal expansion to suspended structural materials such as silicon nitride and silicon oxide. However, the low deposition rate of amorphous-silicon hinders its application in devices that require a suspension gap greater than several micrometres, and chemical stability can be an issue. This paper addresses these issues through the development of a high deposition rate hydrogenated amorphous silicon thin film process. We have demonstrated two unique processing regimes, which can support either a low or high temperature process. The low-temperature processes can be used to deposit silicon thin films at temperatures from room temperature up to 100°C, with deposition rates as high as 0.2  $\mu$ m/min. The high-temperature recipes, deposited at temperatures at and above 200°C, have a slightly lower deposition rate of 0.14  $\mu$ m/min, but are found to be chemically resistant to etching in positive photoresist developer. [2016-0273]

Index Terms—Amorphous silicon, inductively coupled plasma chemical vapour deposition, microelectromechanical systems, sacrificial layer.

# I. INTRODUCTION

THE FABRICATION of application specific microelectromechanical systems (MEMS) utilising surface micromachining relies on the ability to select and use a variety of thin-film materials as the structural layer to achieve the desired electrical, mechanical and/or optical properties. For example, the structural layer of radio frequency (RF) MEMS switches can be made of nickel [1] or a dielectric material with aluminum electrodes [2], whereas MEMS chemical sensors typically use silicon/silicon nitride cantilevers or beams coated

Manuscript received November 9, 2016; revised December 22, 2016; accepted January 6, 2017. Date of publication January 26, 2017; date of current version March 31, 2017. This work was supported in part by the Australian Research Council, Panorama Synergy Ltd., and in part by the Office of Science of the WA State Government. Subject Editor P. M. Sarro.

M. Zawierta, M. Martyniuk, R. Jeffery, G. Putrino, K. K. M. B. D. Silva, and L. Faraone are with the School of Electrical, Electronic and Computer Engineering, University of Western Australia, Crawley, WA 6009, Australia.

A. Keating is with the School of Mechanical and Chemical Engineering, University of Western Australia, Crawley, WA 6009, Australia.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JMEMS.2017.2651110

with a selective sensing layer [3], [4]. A crucial step in the fabrication of surface-MEMS is the release of a freestanding structure that relies on selective removal of the sacrificial layer underlying the structural layer [5]. The wide variety of structural materials require the availability of process compatible sacrificial materials and release processes with high etch-selectivity between the structural and sacrificial layers. In addition to process compatibility, the sacrificial layer must not negatively impact on the stress of the deposited structural layer in order to avoid unwanted deformation of the free standing structure [6], [7]. To achieve this, the sacrificial layer must be chemically stable, non out-gassing [8], and must match both the intrinsic stress and thermal expansion coefficient of any underlying and/or overlying materials.

Amorphous [9], polycrystalline [10] and silicon [11], and more recently silicon [12], have all been used as thin film structural layers to create suspended structures. Amorphous silicon [13] and porous silicon [14], [15] can also be used as sacrificial layers, for example, in the surface-micromachining of CMOS compatible tuneable RF capacitors where the sacrificial layer is a sputtered amorphous silicon film [16]. An important requirement of sacrificial layers in certain applications is the ability to achieve large suspension gaps. In resonant operation, squeezed film damping limits the quality factor, thus requiring either high vacuum or suspension gaps greater than 10  $\mu$ m [17]. For bio-sensing applications, where sensing requires infiltration of cells of up to 10  $\mu$ m in size, large gaps are also required [18]. However, the low deposition rate of amorphous silicon makes it extremely time consuming to achieve large release gaps greater than several micrometres, and the chemical stability of both amorphous and porous films can be an issue.

This work presents a process for high deposition rate amorphous silicon for use as a thick sacrificial layer, using an inductively coupled plasma chemical vapour deposition (ICPCVD) process with a heated substrate. A significant advantage of this process is the high deposition rate (>120 nm/min), which is higher than previously reported ICPCVD processes (up to 90 nm/min) [19]–[23]. However, it is possible to achieve significantly higher deposition rates using microwave chemical vapour deposition processes (MWCVD),

TABLE I

PROCESS STEPS IN THE SILICON DEPOSITION RECIPE [APC VALVE = AUTOMATIC PRESSURE CONTROL VALVE, WHICH CAN BE SET IN THE RANGE OF 0-100%; RF Power = Power of the RF Generator Driving the Heated Table; ICP Power = Power of the RF Generator Driving Inductively Coupled Antenna]

| Step name |                           | SiH <sub>4</sub> flow | Ar flow | Chamber pressure | APC valve | RF power | ICP power | Time    |

|-----------|---------------------------|-----------------------|---------|------------------|-----------|----------|-----------|---------|

| 1:        | Temperature stabilization | 0 sccm                | 0 sccm  | 0 mTorr          | OPEN      | 0 W      | 0 W       | 30 min. |

| 2:        | Gas flow                  | 30 sccm               | 30 sccm | 12 mTorr         | 48 %      | 0 W      | 0 W       | 30 sec. |

| 3:        | Plasma strike, phase 1    | 30 sccm               | 30 sccm | 12 mTorr         | 48 %      | 10 W     | 50 W      | 5 sec.  |

|           | Plasma strike, phase 2    | 30 sccm               | 0 sccm  | 5 mTorr          | OPEN      | 10 W     | 150 W     | 2 sec   |

|           | Plasma strike, phase 3    | 30 sccm               | 0 sccm  | 5 mTorr          | OPEN      | 0 W      | 200 W     | 2 sec   |

| 4:        | Silicon deposition        | 30 sccm               | 0 sccm  | 5 mTorr          | OPEN      | 0 W      | 300 W     | 30 min. |

up to 380 nm/min [24], [25], or hot wire chemical vapour deposition (HWCVD), up to 780 nm/min [26]. But these alternative processes require deposition temperature of at least 250 °C. The high deposition rate enables deposition of nominally 10  $\mu$ m thick sacrificial layers within 2 hours, which is well within the typical processing times for surface-MEMS structures containing multiple layers. The proposed silicon sacrificial layer is ideal for fabrication of MEMS devices on small samples, where spin-coating techniques for sacrificial layers tend to produce a significant edge bead which cannot be easily removed. In addition, MEMS devices fabricated with a thick ICPCVD silicon sacrificial layer can be released using simple wet chemical etching in tetramethyl ammonium hydroxide (TMAH) or potassium hydroxide (KOH) solutions, as well as using dry etching via XeF<sub>2</sub> vapour [27]–[29] or SF<sub>6</sub> plasma [30]. The variety of release methods, which can be used with the proposed sacrificial layer material, allows high selectivity to most modern structural layer materials including silicon oxide, silicon nitride and most metals.

## II. DEPOSITION PROCESS

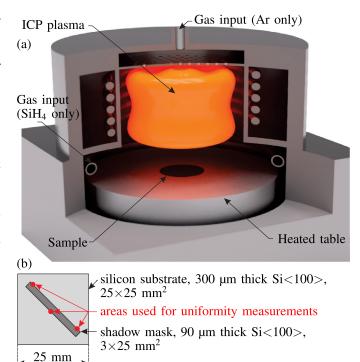

The deposition of amorphous silicon thin films was performed using an Oxford Instruments Plasmalab System 80+, which uses two 13.56 MHz RF generators. The deposition recipe is shown in Table I and contains four main steps. The process commences with temperature stabilization of the sample (30 min) followed by a gas flow step (30 sec) to stabilize the chamber pressure and gas composition. Two gasses are metered into the chamber; SiH4 is delivered through a bottom gas ring while argon is delivered through a gas shower above the ICP antenna, as depicted in Fig. 1(a). Argon is used to assist in striking the plasma and is switched off during deposition [31]. A 3-phase plasma strike procedure is required to start and stabilize the low-pressure pure silane plasma.

During deposition, the ion energy (DC bias) depends on the RF generator power connected to the heated table, whereas the ion current (plasma density) is controlled by the RF generator power connected to the inductively coupled antenna [32]. During the main stage of the silicon deposition, only one RF generator was used, with the RF generator connected to the heated table being switched off to minimize the ion energy,

Fig. 1. (a) Schematic view of Oxford Instruments Plasmalab System 80+ deposition chamber, (b) The adopted general arrangement of the test sample with 90  $\mu$ m thick silicon shadow mask and marked points for measurements of thickness uniformity of film deposited on the 25×25 mm² underlying silicon sample area.

since low ion energy helps in avoiding formation of thin films with significant in-build compressive stress. The high deposition rate can be obtained by adjusting a few variables: gas composition, ICP power, and power to the RF generator connected to the heated table (DC bias). To achieve high deposition rate, we maximize the ICP power [33] and minimize the RF power connected to the heated table (DC bias) [34]. For this experiment, we used the maximum value of ICP power and the maximum flow of SiH<sub>4</sub> available in the tool in order to maximize deposition rate [35].

All depositions were conducted on 300  $\mu$ m thick,  $25 \times 25 \text{ mm}^2 \text{ silicon } \langle 100 \rangle \text{ substrates coated with a 100 nm}$  thick  $\text{SiO}_x$  film, which was used to separate the deposited silicon from the substrate. Before deposition, a 90  $\mu$ m thick

strip of silicon was placed on the substrate as a shadow mask (Fig. 1(b)). The resulting step in the film deposited on the 300  $\mu$ m thick substrate was used to measure the thickness of the layer, and the 90  $\mu$ m thick silicon strip with the deposited film was used for stress measurement of the deposited silicon film via stress induced substrate curvature [36]. All depositions were of 30 min duration. In order to investigate the effect of substrate temperature on the film properties, the heated table temperature was controlled to a fixed value between 25 °C and 300 °C during deposition.

#### III. RESULTS AND DISCUSSION

The deposited silicon thin films were characterized to assess material parameters relevant to the film being used as a sacrificial layer. The properties to be evaluated included deposition rate, film thickness and uniformity, stress, Young's modulus, hardness, surface roughness and chemical resistance to positive photoresist developer. In all cases, no visible defects were observed in the deposited thin films using optical microscopy. As the proposed recipe is intended to be used as a thin film for sacrificial layers in MEMS devices, the void density of the deposited films was not extensively investigated.

## A. Deposition Rate and Thickness Uniformity

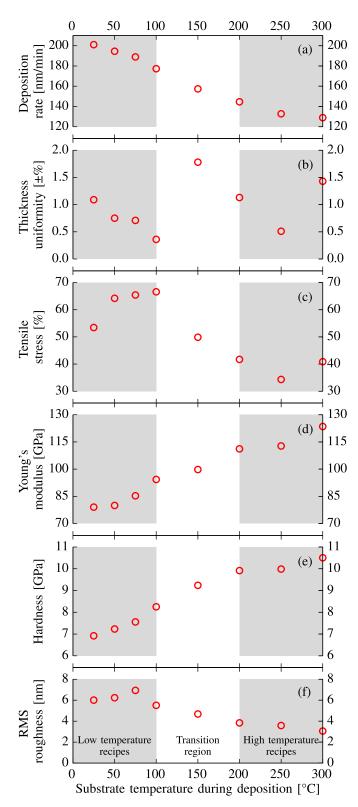

Film thickness (ranging from 4  $\mu$ m to 6  $\mu$ m) was measured using a Veeco Dektak 150 stylus profilometer. Measurements were made in three regions, distributed over the area of the  $25 \times 25 \text{ mm}^2$  sample as indicated in Fig. 1(b), and used to assess both deposition rate and thickness uniformity. These parameters are shown in Fig. 2(a,b) as a function of deposition temperature, where the average deposition rate is seen to monotonically decrease with increasing substrate temperature from a value of 201 nm/min observed for the film deposited at 25 °C to 129 nm/min for the film deposited at 300 °C, as shown in Fig. 2(a). It is a common observation for low pressure ICPCVD processes in this temperature range that as the deposition temperature increases the film density also increases. This can explain the noticeable decrease in deposition rate with increasing substrate temperature, given that the deposition process is consuming a similar amount of silicon radicals at all deposition temperatures, but results in progressively denser, and therefore thinner layers with increasing deposition temperature. Similar behaviour has been observed previously by Nominanda et al. [37] and Jeong et al. [38] for plasma enhanced chemical vapour deposition (PECVD) processes.

In the low-temperature regime below 100 °C, thickness variation decreased with increasing temperature and was measured via Dektak to always be better than  $\pm 1.09\%$ . An abrupt change in thickness uniformity is observed at a substrate deposition temperature of 150 °C and, as such, we use this temperature to define the transition from a low-temperature process to a high temperature process. Low-temperature recipes produced silicon thin films that could be etched in positive photoresist developer and achieved high deposition rates, allowing a 15  $\mu$ m thick sacrificial layer to be deposited in 75 minutes at 25 °C. High-temperature recipes produced silicon films that were stable in positive photoresist developer but with lower

Fig. 2. Thin film (a) deposition rate, (b) thickness uniformity, (c) stress estimation, (d) Young's modulus, (e) hardness, and (f) RMS surface roughness for amorphous silicon as a function of substrate temperature during deposition.

deposition rates, requiring 2 hours to achieve the same 15  $\mu$ m thick sacrificial layer at 300 °C. Relative to all other deposited films, the film thickness variation for 150 °C depositions was found to be the highest ( $\pm 1.78\%$ ) and was consistently lower

for thin films deposited above 150 °C. The reported change in the thickness uniformity is as we observed in our measured data (one sample, three separate measurements). The variation of the thickness is within the specification of the tool of <6% over a 2" diameter sample. This change may not be fully associated with the change in deposition temperature but may also reflect tool variation.

The ICPCVD silicon deposition process can be limited by surface-reactions [5] and/or by the density of available radicals in the plasma [39]. For a process that is limited by surface-reactions excess radicals are present in the chamber which can result in the formation of powder-like polymerized disilane (SiH<sub>2</sub>) particles [39]. This is a common observation for higher pressure silicon deposition processes [40]. The deposition recipes investigated in this work were specifically chosen so as to avoid powder formation within the chamber, suggesting that the deposition rates were limited by the available radicals in the plasma. Once the process conditions were achieved that did not result in powder formation in the chamber, the density of available radicals in the plasma was kept constant by ensuring the pressure, gas flow, and RF power were all kept constant.

#### B. Thin Film Stress Estimation

In many applications, the stress of released thin films needs to be minimized. This necessitates matching the stress of the sacrificial layer and the structural thin film allowing the deformation of any free standing structures to be minimized during the release process [6], [7].

The stress of thin film amorphous silicon layers studied in this work was estimated using thin film stress induced substrate bending and Stoney's formula [36]. The curvatures of the 90  $\mu$ m thick silicon strips with dimensions of  $3 \times 25 \text{ mm}^2$  were measured before and after depositions of the amorphous silicon thin films using a Zygo NewView white light optical surface profilometer. Figure 2(c) shows the resulting stress estimation as a function of substrate deposition temperature. It should be noted that in all cases a relatively low value of intrinsic tensile stress was found (<70 MPa). Not only is tensile stress preferred over compressive stress whenever it is desirable to create flat suspended beams and plates, but the observed magnitude of the stress is considerably lower than for hydrogenated amorphous silicon films deposited using PECVD or RF glow discharge. Yin et al. [41] reported compressive stress values in the range from 300 MPa to 800 MPa for hydrogenated amorphous silicon prepared via plasma-enhanced chemical vapour deposition (PECVD). Harbison et al. [42] reported compressive stress values in the range from 50 MPa to 800 MPa for hydrogenated amorphous silicon thin films deposited using RF glow discharge.

#### C. Young's Modulus and Hardness

The Young's modulus and indentation hardness of the samples were estimated via the nanoindentation technique [43] using a Hysitron TI 950 TriboIndenter instrument and a Berkovich indentation tip [44]. Each amorphous silicon thin

film sample was indented with 5 sets of 30 indents with loading progressively increasing from 0.5 mN to 10 mN. The Young's modulus and hardness of the material were calculated using the Oliver and Pharr method [45], where the penetration depth exceeded 50 nm [46], [47]. During the calculations we assumed  $\nu_{\rm silicon} = 0.278$  [48],  $\nu_{\rm indenter} = 0.07$ , and  $E_{\rm indenter} = 1140$  GPa [46]. The obtained Young's modulus and hardness values are shown in Fig. 2(d,e) as a function of substrate deposition temperature.

The generally high Young's modulus and hardness values observed, especially for deposition at the highest temperature (300 °C), are comparable with values reported in the literature for high quality thin film silicon layers. Jiang *et al.* [49] reported values of Young's modulus up to 100 GPa and hardness up to 10 GPa for sputtered amorphous hydrogenated silicon. In comparison, Bhushan *et al.* [50] measured a Young's modulus of 179 GPa and a hardness for undoped crystalline silicon (100) of 13 GPa.

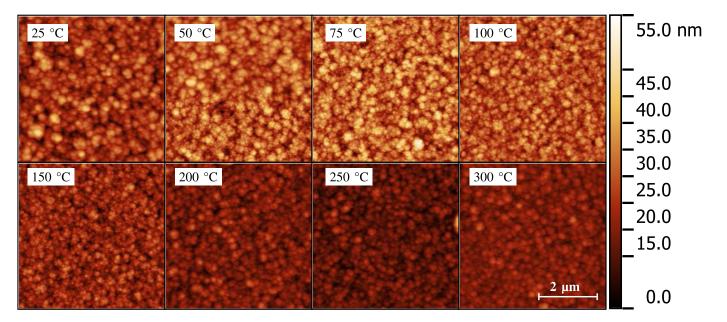

# D. Surface Roughness

The root-mean-squared (RMS) surface roughness of the samples was calculated from  $5 \times 5 \mu m^2$  surface profile images of the silicon films acquired using a WITec alpha 300RA+ atomic force microscope (AFM), and calculated using WITec Project FOUR software, version 4.0. Figure 3 shows the AFM images of the amorphous silicon thin film surfaces obtained for films prepared at the investigated deposition temperatures, and the RMS surface roughness values are shown in Fig. 2(f) as a function of deposition temperature. The surface roughness was found to decrease with increasing substrate deposition temperature, with the highest surface roughness (6.9 nm) observed for a deposition temperature of 75 °C, and the lowest value (3.1 nm) occurred for a substrate temperature of 300 °C. The results indicate that more robust films (lower RMS surface roughness, higher Young's modulus and higher indentation hardness) are formed at higher substrate deposition temperatures. For use as a sacrificial layer, the most important parameter can often be the RMS surface roughness, since any subsequently deposited layers will conform to the same degree of roughness [51]. Thus, the surface roughness needs to be minimized, especially for MEMS optical surfaces, in order to achieve adequate performance. For optical MEMS, the maximum acceptable level of surface roughness is often given as  $\lambda/20$  [52]–[56]. For example, for devices operating at a wavelength of 1550 nm, the surface roughness value needs to be <78 nm. Surface roughness values observed in this study are significantly below this limit.

### E. Chemical Resistance to Positive Photoresist Developer

The amorphous silicon thin films deposited at low temperatures were found to be readily etched in a positive photoresist developer. Chemical resistance to positive photoresist developer is important if any subsequent photolithography process is required to be undertaken directly on the sacrificial layer. Chemical resistance to developer was determined by immersing samples in Microchem AZ326, an aqueous solution of 2.38% TMAH. Initially, samples were immersed in the

Fig. 3. AFM images of surfaces of amorphous silicon thin films deposited at different substrate temperatures. The indicated scales are common to all images.

developer for 5 minutes, and the thickness change of the amorphous silicon layer was measured using a Veeco Dektak 150 stylus profilometer. Next, the immersion was repeated twice, each time for an additional 10 minutes. The amorphous silicon samples deposited at temperatures up to 100 °C were found to be completely etched away during the first 5 minute immersion. The sample with a deposition temperature of 150 °C was partially etched over the same 5-minute duration, and had a resulting rough surface. In contrast, amorphous silicon samples deposited at temperatures of 200 °C and above were found to be chemically stable and not etched in positive photoresist developer, even after a total immersion time of 30 minutes. Not surprisingly, samples with higher hardness were found to be more resistant to etching in positive photoresist developer.

It was found by Haller et al. [57] that hydrogenated amorphous silicon etch rate can be directly and positively correlated with hydrogen content in deposited material. It is expected that total hydrogen content in films deposited at lower temperatures (up to 100 °C) is significantly higher in comparison to films deposited at 150 °C and above. Moravej et al. [58] reported a change from 6.0 at% to 3.0 at% total hydrogen content in amorphous silicon thin films for a deposition temperature change from 100 °C to 150 °C; and the hydrogen content in films prepared in the temperature range from 25 °C to 100 °C is expected to be even larger. For temperatures above 150 °C, Moravej et al. [58] found that the density of the films increases significantly as the deposition temperature is increased, and this may be due to a decrease in hydrogen content in the form of SiH<sub>2</sub> with increasing deposition temperature. Based on this, we correlate the expected excessive hydrogen concentration of films deposited in the low temperature regime with their ability to be etched in positive photoresist developer.

It was found by Jiang et al. [49] that hydrogen content in silicon thin films can be directly correlated with

Young's modulus and indentation hardness. That can be further explained by the work of Moravej *et al.* [58], who reported that films deposited at lower temperatures contain a significantly higher void density. The presence of voids can imply the lower values of both Young's modulus and indentation hardness observed for films deposited in low deposition temperature regime as compared to high deposition temperature regime. A summary of all the experimental results along with the observed film chemical resistance are tabulated in Table II, and compared to selected literature reports for high quality silicon films. These results confirm the high quality of the silicon thin films developed in the course of this study.

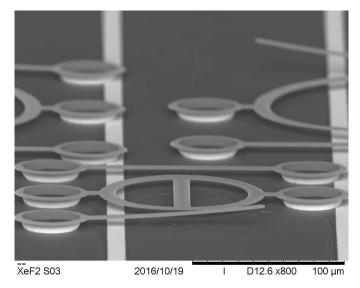

# F. Example of Fabricated Structures Using Amorphous Silicon as a Sacrificial Layer

To demonstrate the use of the developed process recipes in surface micromachining, test micro-structures were fabricated and investigated. The test devices were fabricated using a silicon nitride/gold structural thin film bilayer and a hightemperature amorphous silicon sacrificial layer. Structures were fabricated on a silicon substrate wafer covered with 100 nm thick SiO<sub>x</sub>, and 50 nm thick gold metal pads were deposited for electrostatic actuation of fabricated devices. A 6  $\mu$ m thick amorphous silicon sacrificial layer was deposited at a temperature of 300 °C to minimize surface roughness. We tested depositions up to 1 hour long, creating 12  $\mu$ m thick films. The deposition rate was constant in these tests and did not change with time. Subsequently, the sacrificial layer was patterned using reactive-ion etching (RIE). On top of the sacrificial layer a 50 nm thick film of gold and 700 nm thick film of SiN<sub>x</sub> were deposited and patterned to form the structural layer.

All of the amorphous silicon thin films investigated in this work can be etched by using dry chemical etching in  $XeF_2$  vapour, with etch rates up to 2  $\mu$ m/min in the vertical direction

TABLE II

SUMMARY OF THE MEASURED MATERIAL PROPERTIES FOR ICPCVD SILICON THIN FILMS PREPARED USING LOW- AND HIGH-TEMPERATURE RECIPES

|                                                       | Low temperature recipe | High-temperature recipe | Comparison with literature reports |                     |  |

|-------------------------------------------------------|------------------------|-------------------------|------------------------------------|---------------------|--|

|                                                       | (25 °C – 100 °C)       | (200 °C – 300 °C)       | Deposition technique               | Reported values     |  |

|                                                       |                        | 128 – 144               | ICPCVD [19]                        | 60 – 75 nm/min [19] |  |

|                                                       |                        |                         | ICPCVD [20]                        | ~36 nm/min [20]     |  |

|                                                       |                        |                         | ICPCVD [21]                        | 36 – 84 nm/min [21] |  |

| Deposition rate [nm/min]                              | 177 – 201              |                         | ICPCVD [22]                        | 90 nm/min [22]      |  |

| Deposition rate [min/min]                             |                        |                         | ICPCVD [23]                        | 65 nm/min [23]      |  |

|                                                       |                        |                         | MWCVD [24]                         | 282 nm/min [24]     |  |

|                                                       |                        |                         | MWCVD [25]                         | 380 nm/min [25]     |  |

|                                                       |                        |                         | HWCVD [26]                         | 780 nm/min [26]     |  |

| Thickness uniformity [±%]                             | 0.36 - 1.09            | 0.51 - 1.43             | ICPCVD [59]                        | ±6% over            |  |

| Thickness uniformity [±70]                            | 0.30 - 1.09            |                         | [CFC VD [39]                       | 50 nm area [59]     |  |

|                                                       |                        | 34 – 42                 |                                    | compressive:        |  |

| Thin film tensile stress [MPa]                        | 54 – 67                |                         | PECVD [41]                         | 300 – 800 MPa [41]  |  |

|                                                       |                        |                         | RF glow discharge CVD [42]         | 50 – 800 MPa [42]   |  |

| Young's modulus [GPa]                                 | 79 – 94                | 111 – 123               | low pressure CVD [49]              | up to 100 GPa [49]  |  |

| Indentation hardness [GPa]                            | 6.9 - 8.3              | 9.9 – 10.5              | low pressure CVD [49]              | up to 10 GPa [49]   |  |

| RMS surface roughness [nm]                            | 5.5 - 6.9              | 3.1 – 3.8               | _                                  | _                   |  |

| Chemical resistance to positive photoresist developer | No                     | Yes                     | -                                  | -                   |  |

Fig. 4. SEM image of released micro-structures using silicon as the sacrificial layer (cantilevers, double-supported beams and Guckel rings) suspended 6  $\mu$ m above the substrate. The silicon nitride/gold structures are fabricated on silicon oxide coated substrate and released using chemical dry etching in XeF<sub>2</sub> vapour.

and up to 4  $\mu$ m/min in the horizontal direction [27]–[29], SF<sub>6</sub> plasma with etch rates up to 15  $\mu$ m/min [30], or heavily concentrated and heated TMAH and KOH solutions, with etch rates up to 1.4  $\mu$ m/min (e.g., Tabata *et al.* [60] used a solution of 22 wt% TMAH at 90 °C, and Shikida *et al.* [61] used a solution of 34.0 wt% KOH at 71 °C). In our studies, the fabricated structures were released using chemical dry etching in XeF<sub>2</sub> vapour. The test structures included cantilevers and double-supported beams with dimensions of 10  $\mu$ m × 220  $\mu$ m. Guckel rings were also fabricated with diameter ranging from 90  $\mu$ m to 210  $\mu$ m with a beam width of 10  $\mu$ m as shown in Fig. 4. The release process using XeF<sub>2</sub> etching took less than 5 minutes for the fabricated structures.

#### IV. CONCLUSIONS

We have demonstrated high quality amorphous silicon thin films deposited with high deposition rates using an ICPCVD process, which readily allows control over material properties important for micromachining of MEMS structures. All deposited films can be used for optical MEMS due to the low RMS surface roughness. The achieved low tensile stress (<70 MPa) is an initial requirement in order to minimize the influence of the sacrificial layer on subsequently-deposited structural materials. We achieved a high thickness uniformity ranging from  $\pm 0.36\%$  to  $\pm 1.78\%$  across the full deposition temperature range of 25 °C to 300 °C. Overall, the achieved material parameters allow the use of the investigated films as a sacrificial layer for fabrication of MEMS devices, especially in situations where a suspension gap greater than several micrometers is a necessary requirement.

#### ACKNOWLEDGMENTS

This work was performed in part at the Western Australian and Queensland nodes of the Australian National Fabrication Facility, a company established under the National Collaborative Research Infrastructure Strategy to provide nano and microfabrication facilities for Australia's researchers. The authors acknowledge the facilities, and the scientific and technical assistance of the Australian Microscopy & Microanalysis Research Facility at the Centre for Microscopy, Characterisation & Analysis, The University of Western Australia, a facility funded by the University, State and Commonwealth Governments.

#### REFERENCES

- S. P. Pacheco, L. P. B. Katehi, and C. T.-C. Nguyen, "Design of low actuation voltage RF MEMS switch," in *IEEE MTT-S Int. Microw. Symp. Dig.*, vol. 1. Jun. 2000, pp. 165–168.

- [2] G. M. Rebeiz and J. B. Muldavin, "RF MEMS switches and switch circuits," *IEEE Microw. Mag.*, vol. 2, no. 4, pp. 59–71, Dec. 2001.

- [3] V. A. T. Dam, D. Wouters, W. Knoben, S. H. Brongersma, and R. van Schaijk, "Polymer coated MEMS resonator for room temperature NH3 sensing," in *Proc. IEEE Sensors*, Nov. 2014, pp. 194–197.

- [4] J. M. Dell, M. Martyniuk, A. J. Keating, G. M. Putrino, and L. Faraone, "Optical cantilever based analyte detection," U.S. Patent 2012 0218559 A1, Aug. 30, 2012.

- [5] M. J. Madou, Fundamentals of Microfabrication: The Science of Miniaturization, 2nd ed. Boca Raton, FL, USA: CRC Press, Mar. 2002.

- [6] K. J. Winchester and J. M. Dell, "Tunable Fabry-Pérot cavities fabricated from PECVD silicon nitride employing zinc sulphide as the sacrificial layer," J. Micromech. Microeng., vol. 11, no. 5, p. 589, 2001.

- [7] A. Garg, J. Small, X. Liu, A. K. Mahapatro, and D. Peroulis, "Impact of sacrificial layer type on thin-film metal residual stress," in *Proc. IEEE Sensors*, Oct. 2009, pp. 1052–1055.

- [8] A. Bagolini, L. Pakula, T. L. M. Scholtes, H. T. M. Pham, P. J. French, and P. M. Sarro, "Polyimide sacrificial layer and novel materials for post-processing surface micromachining," *J. Microelectromech. Syst.*, vol. 12, no. 4, p. 385. Jul. 2002.

- [9] J.-L. Tissot, F. Rothan, C. Vedel, M. Vilain, and J.-J. Yon, "LETI/LIR's amorphous silicon uncooled microbolometer development," *Proc. SPIE*, vol. 3379, pp. 139–144, Jul. 1998.

- [10] R. T. Howe, B. E. Boser, and A. P. Pisano, "Polysilicon integrated microsystems: Technologies and applications," *Sens. Actuators A, Phys.*, vol. 56, nos. 1–2, pp. 167–177, Aug. 1996.

- [11] M. Mehregany and C. A. Zorman, "Surface micromachining: A brief introduction," MRS Bull., vol. 26, no. 4, pp. 289–290, Apr. 2001.

- [12] X. Sun, A. Keating, and G. Parish, "Released micromachined beams utilizing laterally uniform porosity porous silicon," *Nanosc. Res. Lett.*, vol. 9, no. 1, p. 426, Dec. 2014.

- [13] S. Frederico, C. Hibert, R. Fritschi, P. Fluckiger, P. Renaud, and A. M. Ionescu, "Silicon sacrificial layer dry etching (SSLDE) for freestanding RF MEMS architectures," in *Proc. IEEE 16th Annu. Int. Conf. Micro Electro Mech. Syst. (MEMS)*, Kyoto, Japan, Jan. 2003, pp. 570–573.

- [14] G. Kaltsas and A. G. Nassiopoulou, "Frontside bulk silicon micromachining using porous-silicon technology," *Sens. Actuators A, Phys.*, vol. 65, pp. 175–179, Mar. 1998.

- [15] M. Navarro, J. M. López-Villegas, J. Samitier, J. R. Morante, J. Bausells, and A. Merlos, "Electrochemical etching of porous silicon sacrificial layers for micromachining applications," *J. Micromech. Microeng.*, vol. 7, no. 3, p. 131, 1997.

- [16] R. Fritschi et al., "High tuning range AlSi RF MEMS capacitors fabricated with sacrificial amorphous silicon surface micromachining," *Microelectron. Eng.*, vols. 73–74, pp. 447–451, Jun. 2004.

- [17] M. Bao and H. Yang, "Squeeze film air damping in MEMS," Sens. Actuators A, Phys., vol. 136, no. 1, pp. 3–27, May 2007.

- [18] S. Chan, S. R. Horner, P. M. Fauchet, and B. L. Miller, "Identification of Gram negative bacteria using nanoscale silicon microcavities," *J. Amer. Chem. Soc.*, vol. 123, no. 47, pp. 11797–11798, Nov. 2001.

- [19] C. Jiuxiang, W. Weizhong, J. S. Cherng, and C. Qiang, "High growth rate of microcrystalline silicon films prepared by ICP-CVD with internal low inductance antennas," *Plasma Sci. Technol.*, vol. 16, no. 5, p. 502, May 2014.

- [20] L. Tian, E. Fathi, R. S. Tarighat, and S. Sivoththaman, "Nanocrystalline silicon deposition at high rate and low temperature from pure silane in a modified ICP-CVD system," *Semicond. Sci. Technol.*, vol. 28, no. 10, p. 105004, Oct. 2013.

- [21] H. B. Jeong, K. N. Kim, N. E. Lee, and G. Y. Yeom, "Study of hydrogenated silicon thin film deposited by using dual-frequency inductively-coupled plasma-enhanced chemical-vapor deposition," *J. Korean Phys. Soc.*, vol. 63, no. 6, pp. 1140–1145, Sep. 2013.

- [22] S.-W. Yoo, S.-J. You, J.-H. Kim, D.-J. Seong, B.-H. Seo, and N.-M. Hwang, "Effect of substrate bias on deposition behaviour of charged silicon nanoparticles in ICP-CVD process," *J. Phys. D, Appl. Phys.*, vol. 50, no. 3, p. 035201, 2017.

- [23] G. Nogay, Z. M. Saleh, E. Özkol, and R. Turan, "Vertically aligned Si nanocrystals embedded in amorphous Si matrix prepared by inductively coupled plasma chemical vapor deposition (ICP-CVD)," *Mater. Sci. Eng. B*, vol. 196, pp. 28–34, Jun. 2015.

- [24] Y. Sakuma, L. Haiping, H. Ueyama, and H. Shirai, "High-density microwave plasma for high-rate and low-temperature deposition of silicon thin film," *Vacuum*, vol. 59, no. 1, pp. 266–276, Oct. 2000.

- [25] H. Jia, J. K. Saha, and H. Shirai, "Plasma parameters for fast deposition of highly crystallized microcrystalline silicon films using high-density microwave plasma," *Jpn. J. Appl. Phys.*, vol. 45, no. 2A, p. 666, Feb. 2006.

- [26] Y. Xu, B. P. Nelson, A. H. Mahan, R. S. Crandall, E. Iwaniczko, Q. Wang, and D. L. Williamson, "a-Si:H grown by hot-wire CVD at ultra-high deposition rates," in *Proc. Program NCPV Program Review Meeting*, Denver, CO, USA, Apr. 2000, pp. 199–200.

- [27] H. F. Winters and J. W. Coburn, "The etching of silicon with XeF<sub>2</sub> vapor," Appl. Phys. Lett., vol. 34, no. 1, pp. 70–73, Jan. 1979.

- [28] I. W. T. Chan, K. B. Brown, R. P. W. Lawson, A. M. Robinson, Y. Ma, and D. Strembicke, "Gas phase pulse etching of silicon for MEMS with xenon difluoride," in *Proc. IEEE Can. Conf. Elect. Comput. Eng.*, vol. 3. May 1999, pp. 1637–1642.

- [29] L. R. Arana, N. de Mas, R. Schmidt, A. J. Franz, M. A. Schmidt, and K. F. Jensen, "Isotropic etching of silicon in fluorine gas for MEMS micromachining," *J. Micromech. Microeng.*, vol. 17, no. 2, p. 384, 2007.

- [30] M. Puech, N. Launay, N. Arnal, P. Godinat, and J. M. Gruffat, "A novel plasma release process and a super high aspect ratio process using ICP etching for MEMS," presented at the 6th SEMI Microsyst./MEMS Seminar, 2002, pp. 111–114.

- [31] AzoNano. (Nov. 2010). New Improvements in Inductively Coupled Plasma—Chemical Vapour Deposition (ICP-CVD) Process by Oxford Instruments Plasma Technology, accessed on Jan. 18, 2017. [Online]. Available: http://www.azonano.com/article.aspx?ArticleID=2731

- [32] Inductively Coupled Plasma Chemical Vapour Deposition (ICP CVD)— Oxford Instruments, accessed on Jan. 18, 2017. [Online]. Available: https://www.oxford-instruments.com/products/etching-deposition-and-growth/plasma-etch-deposition/icp-cvd

- [33] B. Y. Moon, J. H. Youn, S. H. Won, and J. Jang, "Polycrystalline silicon film deposited by ICP-CVD," *Solar Energy Mater. Solar Cells*, vol. 69, no. 2, pp. 139–145, Sep. 2001.

- [34] K. D. Mackenzie, J. W. Lee, and D. Johnson, "Inductively-coupled plasma deposition of low temperature silicon dioxide and silicon nitride films for III-V applications," in *Proc. 30th Symp. State-Art Prog. Comp. Semiconductor*, 1999, pp. 1–12.

- [35] AzoMaterials. (Feb. 2012). Deposition of High Quality Films by the Inductively Coupled Plasma CVD Process, accessed on Jan. 18, 2017. [Online]. Available: http://www.azom.com/article.aspx?ArticleID=5953

- [36] G. G. Stoney, "The tension of metallic films deposited by electrolysis," Proc. R. Soc. Lond. A, Math. Phys. Sci., vol. 82, no. 553, pp. 172–175, May 1909.

- [37] H. Nominanda and Y. Kuo, "Process and material properties of PECVD boron-doped amorphous silicon films," in *Proc. ECS Extended Abst.* 14th Int. Plasma Process., 2002, pp. 1–9.

- [38] K.-H. Jeong, S.-G. Park, and S.-W. Rhee, "Nanocomposite low-k SiCOH films by plasma-enhanced chemical vapor deposition using vinyltrimethylsilane and CO<sub>2</sub>," *J. Vac. Sci. Technol. B, Microelectron. Process. Phenom.*, vol. 22, no. 6, pp. 2799–2803, Nov. 2004.

- [39] S. Vepřek, F.-A. Sarrott, S. Rambert, and E. Taglauer, "Surface hydrogen content and passivation of silicon deposited by plasma induced chemical vapor deposition from silane and the implications for the reaction mechanism," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 7, no. 4, pp. 2614–2624, Jul. 1989.

- [40] M. Cooke, "Dust management in silane PECVD systems," in Process News. Bristol, U.K.: Oxford Instruments Plasma Technology, Nov. 2014.

- [41] Y. Yin, D. McKenzie, and M. Bilek, "Intrinsic stress induced by substrate bias in amorphous hydrogenated silicon thin films," Surf. Coatings Technol., vol. 198, nos. 1–3, pp. 156–160, Aug. 2005.

- [42] J. P. Harbison, A. J. Williams, and D. V. Lang, "Effect of silane dilution on intrinsic stress in glow discharge hydrogenated amorphous silicon films," *J. Appl. Phys.*, vol. 55, no. 4, pp. 946–951, Feb. 1984.

- [43] R. F. Bishop, R. Hill, and N. F. Mott, "The theory of indentation and hardness tests," *Proc. Phys. Soc.*, vol. 57, no. 3, p. 147, 1945.

- [44] M. M. Khrushchov and E. S. Berkovich, "Methods of determining the hardness of very hard materials: The hardness of diamond," *Ind. Diamond Rev.*, vol. 11, no. 2, pp. 42–49, 1951.

- [45] W. C. Oliver and G. M. Pharr, "Measurement of hardness and elastic modulus by instrumented indentation: Advances in understanding and refinements to methodology," *J. Mater. Res.*, vol. 19, no. 1, pp. 3–20, Jan. 2004.

- [46] R. Ge et al., "Nanoindentation of Si<sub>1-x</sub>Ge<sub>x</sub> thin films prepared by biased target ion beam deposition," in Proc. Conf. Optoelectron. Microelectron. Mater. Devices, Dec. 2014, pp. 210–213.

- [47] Y.-G. Jung, B. R. Lawn, M. Martyniuk, H. Huang, and X. Z. Hu, "Evaluation of elastic modulus and hardness of thin films by nanoindentation," J. Mater. Res., vol. 19, no. 10, pp. 3076–3080, Oct. 2004.

- [48] L. Gan, B. Ben-Nissan, and A. Ben-David, "Modelling and finite element analysis of ultra-microhardness indentation of thin films," *Thin Solid Films*, vols. 290–291, pp. 362–366, Dec. 1996.

- [49] X. Jiang, K. Reichelt, and B. Stritzker, "The hardness and Young's modulus of amorphous hydrogenated carbon and silicon films measured with an ultralow load indenter," *J. Appl. Phys.*, vol. 66, no. 12, pp. 5805–5808, Dec. 1989.

- [50] B. Bhushan and X. Li, "Micromechanical and tribological characterization of doped single-crystal silicon and polysilicon films for microelectromechanical systems devices," *J. Mater. Res.*, vol. 12, no. 1, pp. 54–63, Jan. 1997.

- [51] S. H. Kim, M. T. Dugger, and K. L. Mittal, Adhesion Aspects in MEMS/NEMS. Boca Raton, FL, USA: CRC Press, Feb. 2011.

- [52] J.-L. Wang, T.-Y. Chen, C. Liu, C.-W. E. Chiu, and G.-D. J. Su, "Polymer deformable mirror for optical auto focusing," *ETRI J.*, vol. 29, no. 6, pp. 817–819, Dec. 2007.

- [53] G. Vdovin and P. M. Sarro, "Flexible mirror micromachined in silicon," Appl. Opt., vol. 34, no. 16, p. 2968, Jun. 1995.

- [54] R. P. Grosso and M. Yellin, "The membrane mirror as an adaptive optical element," *J. Opt. Soc. Amer.*, vol. 67, no. 3, p. 399, Mar. 1977.

- [55] R. Ryf, H. R. Stuart, and C. R. Giles, "MEMS tip/tilt and piston mirror arrays as diffractive optical elements," *Proc. SPIE*, vol. 5894, pp. 58940C-1–58940C-11, Aug. 2005.

- [56] D. A. Horsley et al., "Optical and mechanical performance of a novel magnetically actuated MEMS-based optical switch," J. Microelectromech. Syst., vol. 14, no. 2, pp. 274–284, Apr. 2005.

- [57] I. Haller, Y. H. Lee, J. J. Nocera, Jr., and M. A. Jaso, "Selective wet and dry etching of hydrogenated amorphous silicon and related materials," *J. Electrochem. Soc.*, vol. 135, no. 8, pp. 2042–2045, Aug. 1988.

- [58] M. Moravej, S. E. Babayan, G. R. Nowling, X. Yang, and R. F. Hicks, "Plasma enhanced chemical vapour deposition of hydrogenated amorphous silicon at atmospheric pressure," *Plasma Sour. Sci. Technol.*, vol. 13, no. 1, p. 8, 2004.

- [59] O. Thomas, Inductively Coupled Plasma Chemical Vapour Deposition (ICP-CVD). Bristol, U.K.: Oxford Instruments Plasma Technology, 2010.

- [60] O. Tabata, R. Asahi, H. Funabashi, K. Shimaoka, and S. Sugiyama, "Anisotropic etching of silicon in TMAH solutions," *Sens. Actuators A*, *Phys.*, vol. 34, no. 1, pp. 51–57, Jul. 1992.

- [61] M. Shikida, K. Sato, K. Tokoro, and D. Uchikawa, "Differences in anisotropic etching properties of KOH and TMAH solutions," *Sens. Actuators A, Phys.*, vol. 80, no. 2, pp. 179–188, Mar. 2000.

mechanical systems.

Michal Zawierta was born in Poland, in 1986. He received the B.Sc. and M.Sc. degrees in electronics and telecommunication from the Wroclaw University of Technology, Wroclaw, Poland, in 2011 and 2012, respectively, and the B.Sc. degree in management from the Wroclaw University of Economics, Wroclaw, in 2011. He is currently pursuing the Ph.D. degree with the School of Electrical, Electronic, and Computer Engineering, University of Western Australia, Perth, WA, Australia. His current research activities involve optical microelectro-

Mariusz Martyniuk (M'12) was born in Poland. He received the B.Sc. (Hons.) degree from the University of Toronto, ON, Canada, the M.A.Sc. degree from McMaster University, ON, Canada, and the Ph.D. degree from the University of Western Australia, Perth, Australia, in 2007. He worked in the industry sector as an Electronics Engineer before rejoining The University of Western Australia, where he is currently a Research Professor with the School of Electrical, Electronic and Computer Engineering and manages the Western Australian Node of the

Australian National Fabrication Facility. His primary areas of interest encompass thin-film materials and thin-film mechanics, as well as their applications in micro-electromechanical systems and optoelectronic devices.

Dr. Martyniuk's research contributions were recognized by the award of the Inaugural Australian Museum Eureka Prize (the Oscars of Australian science) for Outstanding Science in Support of Defence or National Security in 2008.

Roger D. Jeffery received the B.Sc. degree in mathematics and computer science, and the B.E. degree from Adelaide University, Adelaide, SA, Australia, in 1972 and 1973, respectively, and the M.Eng.Sc. and Ph.D. degrees from the University of Western Australia (UWA), Crawley, WA, Australia, in 1979 and 1984, respectively.

He joined the Department of Electrical and Electronic Engineering, UWA, in 1973. From 1985 to 1986, he was an ARGC Research Fellow and a member of the original Networking Group in the

Department of Electrical and Electronic Engineering, UWA, where he was involved in QPSX technology, which was subsequently standardized as IEEE 802.6. He was involved in the communications industry and subsequently led several ASIC design teams from 1987 to 2004. He was involved in drivers for magnetooptic material. In 2005, he was a Contractor at ST Synergy Ltd., Perth, WA, Australia, (later becoming Panorama Synergy Ltd.). He was involved in magneto optics until 2015 and held several patent applications in this area. Since 2013, he has been involved in MEMs sensors using an optical readout. He is currently an Adjunct Associate Professor with the School of Electrical, Electronic, and Computer Engineering, UWA.

Gino Putrino was born in Perth, Australia, in 1976. He received the B.Sc. degree in computer science, and the B.E. degree in electrical and electronic engineering from the University of Western Australia, Perth, in 1999, and the Ph.D. degree in 2014. His current research activities involve the use of optical microelectro-mechanical systems and silicon photonics to create novel chemical and biological sensing devices.

Adrian Keating (M'90–SM'07) was born in Melbourne, Australia, in 1967. He received the B.E. degree (Hons.) and the Ph.D. (in photonics) degree in electrical and electronic engineering from the University of Melbourne, Australia, in 1990 and 1995, respectively. Since 1996, he has been with NTT Research Labs, Musashino, Japan; the University of California at Santa Barbara, Santa Barbara; and Calient Networks as the Fiber Optics Technology Manager. He joined the School of Electrical. Electronic. and Computer Engineering with

the University of Western Australia, in 2004, and then with the School of Mechanical Engineering, where he is currently an Associate Professor. His current research activities are in infrared optics sensors, sensor systems, optical microelectromechanical systems, and porous silicon-based sensor technologies.

K. K. M. B. Dilusha Silva (M'08) was born in Sri Lanka, in 1973. He received the degree (Hons.) in physics and electronics engineering, and the Ph.D. degree from the University of Western Australia (UWA), Perth, WA, Australia. He was in the industry and academia, and is currently a Research Professor and Engineering Manager with the Microelectronics Research Group, UWA. His research interests include optical microelectromechanical systems (MEMS) sensors, optical spectroscopic sensors, and MEMS biosensors. He has

attracted research funding from government and the agriculture and aerospace sectors, and he leads a number of MEMS research efforts with strong commercial links to both agriculture and aerospace.

Lorenzo Faraone (M'78–F'15) received the Ph.D. degree from the University of Western Australia (UWA) in 1979. He was a Research Scientist at Lehigh University, USA, from 1979 to 1980. He joined UWA in 1987. He has supervised over 35 Ph.D. student completions and authored over 250 refereed journal papers. His research interests have been in the area of infrared semiconductor materials and devices, and microelectromechanical systems. He is a member of the Order of Australia, and a fellow of the

Australian Academy of Science and the Australian Academy of Technology and Engineering. From 1980 to 1986, he was a Member of Technical Staff at RCA Laboratories, Princeton, NJ, USA, where he was involved in CMOS nonvolatile memory technologies and space radiation effects in silicon-on-sapphire MOS integrated circuits.